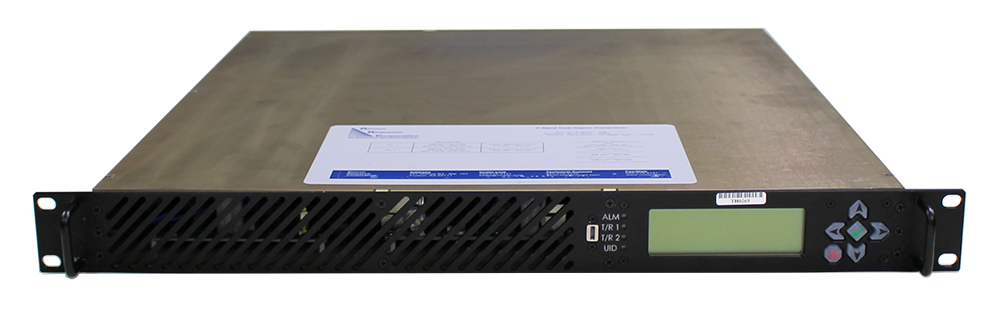

DLSR3

Description

The DLSR3 builds on the DLSR and DLSR2 legacy with an upgraded digitizing architecture enabling continuous frequency coverage from 750 to 2150 MHz, while retaining wideband snapshot, API, and X-Midas option-tree features that have been key elements of the DLSR family for over a decade. The forward-looking DLSR3 design provides new features and capabilities with maximum backwards compatibility.

Using multi-rate signal processing techniques, the DLSR3 digitizes multiple L-band inputs, with up to eight independent digital sub-band tuner outputs per input. Tuner data is provided on multiple 10GbE interfaces for distribution to individual clients or broadcast to multiple recipients. All outputs include high-precision, high-accuracy time tags supporting the most demanding downstream applications.

The DLSR3’s unique wideband snapshot feature provides continuous surveys of the entire digitized input signal (up to 2150 MHz) to support downlink evaluation and signal discovery. Snapshots size (up to 5 GB), output rate, and trigger modes are configurable.

Features

- Extended L-band analog inputs, 750 MHz to 2150 MHz

- Two or four inputs per 1U chassis

- 4800 MSPS, 14-bit interleaved ADC (ENOB: 8 bits)

- Self-calibration and built-in test capabilities

- Programmable input attenuator (0 dB to 31.5 dB)

- Snapshot, histogram, bit-activity, and overload indicators to easily determine input signal levels

- 1PPS, 10 MHz, IRIG-B, and NTP inputs

- Xilinx UltraScale+ MPSoC FPGA with 64-bit processor

- Wideband (4800 MSPS) snapshot capability (up to 5 GB per input)

- Eight digital sub-band tuners (SBTs) per ADC with configurable bandwidths: 80, 40, 20, 10, 5, 2.5 MHz

- Manual and automatic gain controls

- Two SFP+ 10-Gigabit Ethernet outputs per analog input

- SDDS packet format, VITA-49 option coming soon

- 8- or 16-bit, real or complex data formats (SI, SB, CB, CI)

- High-precision data time tags provided for DDC and snapshot outputs

- Command and control via embedded-Linux processor

- Front panel LCD interface for easy setup and configuration

- Boot from local flash storage or network file system (NFS)

- TLS compliant control interface

- X-Midas option tree and Python API included

Documentation

For additional information, download the DLSR3 Product Brief.

Order

Orderable Part Numbers:

DLSR3-1U-2E4X-01

- 2 L-band inputs

- 4 10GbE outputs

DLSR3-1U-4E8X-01

- 4 L-band inputs

- 8 10GbE outputs

DLSR3-MU-DS-01

- METI deathstalker configuration

- Two In, Two Out

Units include two power cords No-cost configuration options include NFS or local boot modes and write-protection on internal flash memories Rack slides and 10GbE output media sold separately.

Contact us for availability and custom configurations.

Orders may be placed via e-mail, telephone, fax, or mail.

Commercial Price List available upon request.

E-mail: sales@rincon.com

Phone: 520-519-3131

Fax: 520-519-3120

Mail: Rincon Research Corporation

Attention: Sales

101 North Wilmot Road, Suite 101

Tucson, AZ 85711

WARNING: Commodities, including associated software, firmware, and technical data, offered for sale on this site are controlled for export by the U.S. Department of State under the International Traffic in Arms Regulations (ITAR) or by the Department of Commerce under the Export Administration Regulations (EAR). Purchaser is required by U.S. law to comply with these regulations. Export, re-export, and retransfer of these commodities by any means without the required licenses or other U.S. Government authorization is prohibited by U.S. law.

Technical Specifications

Power Connector

IC 60320 C14 with NEMA5-15 cord

Power

110/220 VAC 50/60 Hz

Power Consumption, Typical

200 W

2-input

400 W 4-input

Number of Inputs

Two or four

Number of 10GbE Outputs

Two per input, maximum 8

Dimensions

1U 19” rackmount, 26” depth

Operating Temperature

0 to 50 degrees Celcius

Analog Input/Output Levels

-35 dBm (nom), 50 ohm, AC-coupled, 500 MHz to 2150 MHz, SMA connector

0 to 31.5 dB input attenuator, 0.5 dB steps

10 MHz

750 mVpp to 2 Vpp (1.5 dBm to 10 dBm), 50 ohm, AC-coupled, sine wave, SMA connector

1 PPS

CMOS compatible, 50 ohm, SMA connector

Timecode

IRIG-B: 0.5 Vpp to 5 Vpp, 50 ohm, 1 kHz AM, SMA

Control

10/100/1000BASE-T Ethernet, RJ-45 Static or DHCP IP address

10 GbE Output Media

SR Fiber

LR Fiber

Twinax copper patch cables